In an era where large language models (LLMs) are becoming integral to countless applications, from natural language processing to real-time chat systems, the demand for efficient inference has never been more pressing, as the computational intensity of these models often results in significant latency and energy consumption. This is particularly true when relying on traditional GPU-based systems that frequently access off-chip DRAM. A groundbreaking approach has emerged to tackle these inefficiencies, focusing on field-programmable gate arrays (FPGAs) as a viable alternative. By reimagining how data flows through hardware, this innovative solution promises to reshape the landscape of AI inference, delivering faster processing and lower power usage. This development not only addresses current bottlenecks but also paves the way for scalable, sustainable AI deployments in data centers and edge environments.

Revolutionizing AI Workloads with Dataflow Architectures

Shifting Paradigms in Hardware Acceleration

The growing complexity of LLMs necessitates a departure from conventional processing methods that often struggle with latency due to constant data shuttling to and from DRAM. A novel compiler framework has been developed to harness the power of FPGAs, specifically targeting AMD’s Alveo U55C, to optimize inference tasks. Unlike traditional batch-processing approaches, this system introduces a streaming dataflow model that prioritizes on-chip communication. Data moves directly between computational kernels through first-in-first-out (FIFO) buffers, significantly reducing memory round-trips. This paradigm shift not only slashes latency but also boosts energy efficiency, making it a compelling choice for decoding workloads in modern AI applications. The emphasis on streaming intermediates ensures that computational resources are utilized more effectively, addressing a critical pain point in high-performance computing.

Core Innovations Driving Efficiency

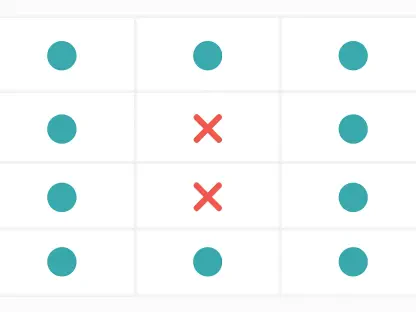

At the heart of this framework lies a unique abstraction known as the iterative tensor (itensor), which redefines how data iteration, tiling, and layout are managed during processing. This abstraction ensures compatibility between kernels for seamless streaming and enables safe kernel fusion, minimizing the need for additional data format converters. When mismatches do occur, the system automatically synthesizes minimal buffers to maintain flow. Furthermore, a hierarchical design space exploration (DSE) method optimizes key parameters like tiling, vectorization, and resource allocation to achieve peak performance under hardware constraints. By employing a linear programming model to size FIFO buffers, the risk of stalls or deadlocks is mitigated while conserving on-chip memory. These technical advancements collectively underscore a forward-thinking approach to AI inference, tailored for the unique capabilities of FPGA hardware.

Bridging High-Level Models to Hardware Deployment

Seamless Compilation for Practical Implementation

One of the standout features of this optimization framework is its end-to-end compilation pipeline, which transforms high-level PyTorch models into hardware-ready kernels without requiring manual intervention. The process begins by ingesting models through Torch-MLIR, converting them into MLIR Linalg, and ultimately mapping them to a dataflow intermediate representation (IR). In this IR, nodes represent hardware kernels with explicit data streams, eliminating the cumbersome task of manual register-transfer level (RTL) design. This automated flow integrates host and runtime support, ensuring that developers can deploy complex LLMs on FPGAs with relative ease. The result is a streamlined path from model design to execution, democratizing access to advanced hardware acceleration for AI practitioners and reducing the barrier to entry for leveraging specialized hardware in real-world scenarios.

Performance Gains and Future Potential

Evaluation of this compiler framework reveals impressive outcomes, particularly in the realm of LLM decoding tasks. Compared to GPU baselines, latency reductions of up to 0.64× have been achieved, alongside energy efficiency improvements peaking at 1.99× against high-end GPUs like NVIDIA’s A100. Even when benchmarked against other FPGA accelerators, latency improvements of 0.76× stand out, highlighting the efficacy of the streaming dataflow design. While the current focus remains on decoding workloads, these results suggest a strong foundation for broader applications in AI inference. The potential to expand this approach to other tasks or hardware platforms remains an exciting avenue for exploration, as the demand for efficient, scalable solutions continues to grow. This framework’s ability to balance performance with resource constraints positions it as a key player in the ongoing evolution of AI hardware optimization.

Reflecting on a Path Forward

Lessons Learned from a Streaming Success

Looking back, the development of this compiler framework marked a pivotal moment in addressing the inefficiencies of traditional LLM inference methods. The adoption of a streaming dataflow model on FPGAs like the Alveo U55C demonstrated that substantial gains in latency and energy efficiency were achievable, with reductions in processing time and power usage that outstripped conventional GPU approaches. The introduction of the itensor abstraction and automated compilation pipeline proved instrumental in simplifying complex hardware optimizations, ensuring that data moved seamlessly between kernels with minimal overhead. These achievements highlighted the value of hardware-software co-design, where tailored compilers played a crucial role in unlocking the full potential of specialized hardware for AI workloads.

Charting the Next Steps for AI Inference

As the landscape of AI continues to evolve, the insights gained from this framework’s implementation offer actionable guidance for future advancements. Expanding the scope beyond decoding to encompass a wider range of LLM tasks stands as a logical next step, potentially broadening its impact across diverse applications. Additionally, adapting the streaming dataflow model to other hardware platforms could further enhance its versatility, ensuring compatibility with emerging technologies. Researchers and engineers are encouraged to build on the foundation of automated compilation and resource optimization, exploring ways to integrate these principles into larger, more complex AI systems. By focusing on scalability and adaptability, the field can move toward more sustainable and efficient inference solutions, ultimately benefiting both industry and end users in an increasingly AI-driven world.